# **COMPOUND** SEMICONDUCTOR **Connecting the Compound Semiconductor Community**

Volume 26 Issue 2 MARCH 2020

🔰 @compoundsemi

www.compoundsemiconductor.net

Comb lasers advance computing power

Finding a better face for the SiC MOSFET

PICs: Plug-and-play characterization

RF GaN: Big revenues, bright future?

**UV LEDs** Smashing efficiency records

**INSIGE** News Review, News Analysis, Features, Research Review, and much more... Free Weekly E News round up go to: www.compoundsemiconductor.net

## Best performance for next generation SiC power electronics to address global mega trends

*BIXTRON*

# AIX G5 WW C

- Electric vehicles: on board chargers, power inverters

- Infrastructure: charging stations

- Renewables: solar and wind

- Industrial: motor drives, power supplies

- Power distribution: HVDC

Discover our SiC epi production batch tool with single wafer performance

Made in Germany

www.aixtron.com

# Viewpoint

By Dr Richard Stevenson, Editor

## Breakthroughs in the deep UV

LEDs that emit in the deep UV are notorious for feeble output powers and incredibly short lifetimes. Both get worse as the wavelength decreases.

However, improvements are possible. Recently, a partnership between researchers at Asahi Kasei Corporation and Crystal IS has unveiled a suite of devices that can operate for over 3000 hours and deliver record efficiencies between 230 nm and 237 nm (see p. 66); and a collaboration between scientists at the University of Science and Technology of China and Huazhong University of Science and Technology has smashed the record for wall-plug efficiency for 280 nm LEDs (see p. 20).

Given that deep UV LEDs have been in development for decades, you would expect that all the latest improvements came through esoteric refinements. But the reality is more complex, involving excelling in the basics, as well as turning to innovation.

It is well known that oxygen is to be avoided in UV LEDs, as it leads to energy-sapping point defects that can move through the device. The team from Kasei Corporation and Crystal IS have driven this down by investing in a more modern MOCVD reactor, optimising the growth conditions and turning to sources with greater purity. All these moves are thought to have lengthened the lifetime of their devices.

After thinning their UV-emitting chips and mounting them in a transparent flip-chip package, the team are getting output powers of just over a milliwatt at 100 mA drive currents. That's an improvement, but external quantum efficiencies and wall-plug efficiencies are still well below one percent.

Why are they so low? It's primarily because as emission wavelengths head towards the deep UV, extraction efficiencies plummet, with much of the light failing to exit the chip. The team is now proposing a novel solution to address this: extract the emission from the edge of the chip.

For the team from China, a radical architecture is behind the record-breaking wall-plug efficiencies – they are a whopping 20 percent for their 280 nm emitters. In their design, a conventional LED is monolithically united with a photoelectric converter that multiplies holes by impact ionisation, before these carrier are re-injected into the active region.

While this team's success is driven by a trail-blazing architecture, they have also worked hard to address many of the wellknown weaknesses in the UV LED. They grow device layers on a patterned sapphire with a silica array, as this reduces dislocations in the materials an aids light extraction; and they turn to mis-cut substrates to reduce the internal electric fields that pull apart electrons and holes. So they get the basics right, and use this as a strong foundation for their innovation.

| Editor Richard Stevenson<br>Contributing Editor Rebecca Pool | richardstevenson@angelbc.com<br>editorial@rebeccapool.com | +44 (0)1291 629640 | Circulation Director Scott Adams<br>Chief Executive Officer Stephen Whitehurst                      | scott.adams@angelbc.com<br>stephen.whitehurst@angelbc.cc | +44 (0)2476 718970          |

|--------------------------------------------------------------|-----------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------|

| News Editor Christine Evans-Pughe                            | chrise-p@dircon.co.uk                                     |                    |                                                                                                     | otophoninininonalot(e aligoiboloc                        |                             |

| Sales Executive Jessica Harrison                             | jessica.harrison@angelbc.com                              | +44 (0)2476 718970 | Joint Managing Director Sukhi Bhadal                                                                | sukhi.bhadal@angelbc.com                                 | +44 (0)2476 718970          |

| USA Representatives Brun Media                               |                                                           |                    | Joint Managing Director Scott Adams                                                                 | scott.adams@angelbc.com                                  | +44 (0)2476 718970          |

| Tom Brun                                                     | tbrun@brunmedia.com                                       | +001 724 539-2404  | Directors Jackie Cannon, Sharon Cowley                                                              |                                                          |                             |

| Janice Jenkins                                               | jjenkins@brunmedia.com                                    | +001 724-929-3550  | Published by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, |                                                          |                             |

| Publisher Jackie Cannon                                      | jackie.cannon@angelbc.com                                 | +44 (0)1923 690205 | Coventry CV5 6SP, UK. T: +44 (0)2476 718 970                                                        | ) E: info@angelbc.com                                    |                             |

| Director of Logistics Sharon Cowley                          | sharon.cowley@angelbc.com                                 | +44 (0)1923 690200 |                                                                                                     |                                                          | _                           |

| Design & Production Manager Mitch Gaynor                     | mitch.gaynor@angelbc.com                                  | +44 (0)1923 690214 |                                                                                                     | Angel 🚫 🄇                                                | recycle                     |

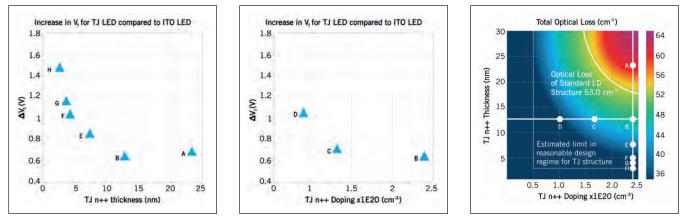

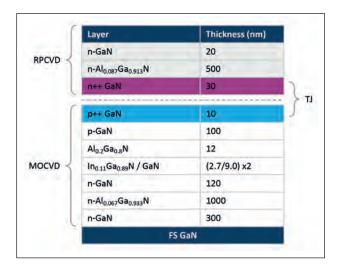

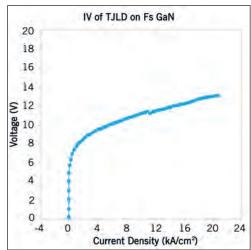

|                                                              |                                                           |                    |                                                                                                     | BUSINESS COMMUNICATIONS                                  | When you have finished with |

Compound Semiconductor is published eight times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £105.00/e158 pa (UK & Europe), £138.00 pa (air mail), \$198 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subsequent issue of the publisher. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information: Compound Semiconductor, ISN 1096-598X, is published 8 times a year, Jan/Feb, March, April/May, June, July, August/September, October, November/ December by Angel Business Communications Ltd, Unit 6, Bow Court, FletChworth Gate, Burnsall Rd, Coventry CV5 6SP (K. The 2020 US annual subscription price is \$198. Airfreight and mailing in the USA by agent named Air Business Ltd, c/o WN Shipping USA, 156-15, 146th Avenue, 2nd Floor, Jamaica, NY 11434, USA. Prinded by: The Manson Group. ISSN 1096-598X (Print) ISSN 2042-7328 (Online) © Copyright 2020.

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if they recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time or the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organisation, or engage with them for future commercial enterprise.

### 20 COVER STORY

#### A massive boost for UV LED efficiency

The monolithic integration of a conventional LED structure and a multiplicative photoelectric converter propels the wall-plug efficiency of deep UV LEDs emitting at 280 nm to more than 20 percent

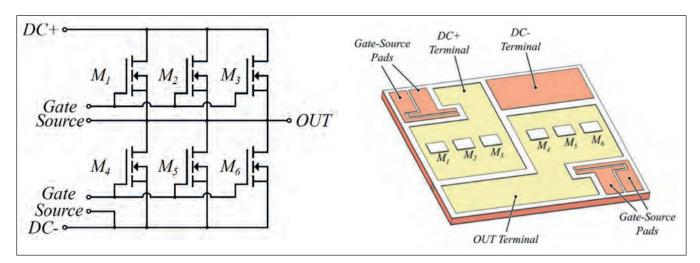

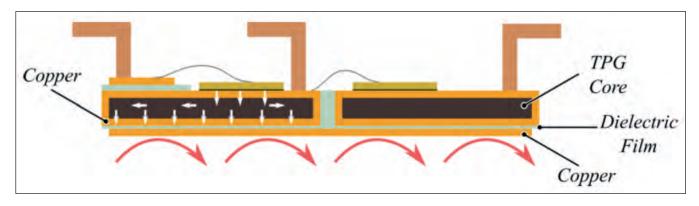

#### 28 Comb lasers advance high-performance computers

By tackling a bottleneck in bandwidth, multiwavelength quantum dot lasers are enabling improvements in high-performance computers

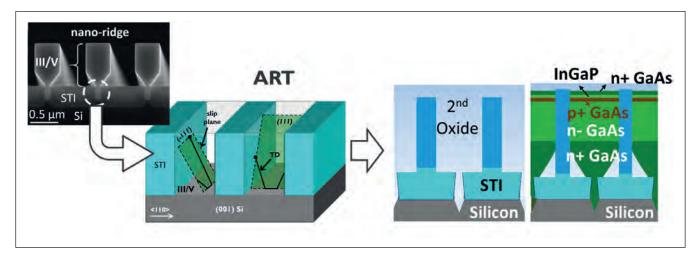

#### 36 Uniting III-Vs with silicon for beyond-5G front-end modules

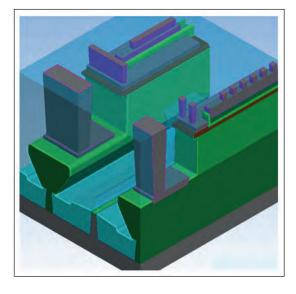

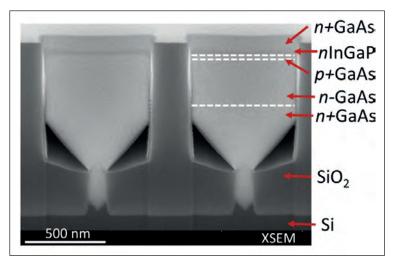

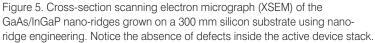

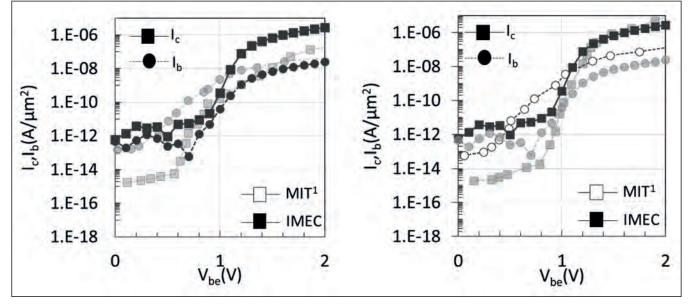

Combining aspect ratio trapping with nano-ridge engineering enables 300 mm substrates to provide a platform for the fabrication of GaAs/InGaP HBTs that deliver amplification in the millimetre-wave

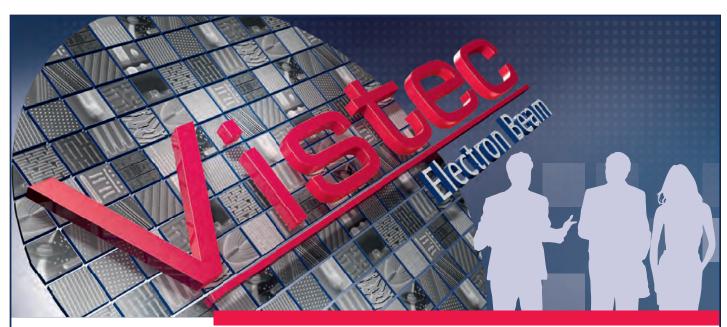

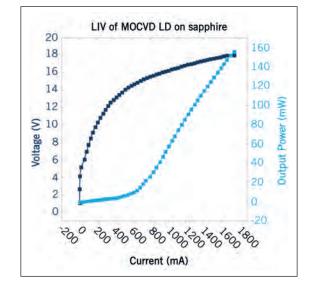

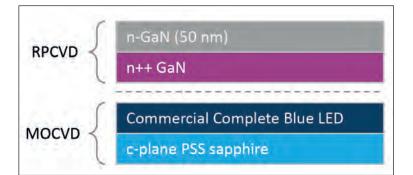

#### 42 Hybrid growth promises better performing laser diodes

Adding tunnel junctions by remote-plasma CVD will lead to more-powerful, more-efficient GaN lasers

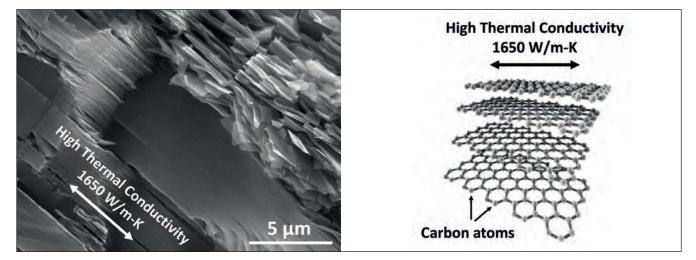

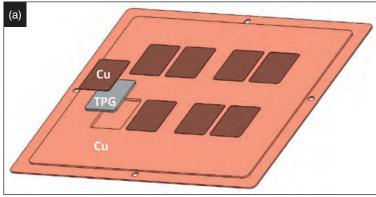

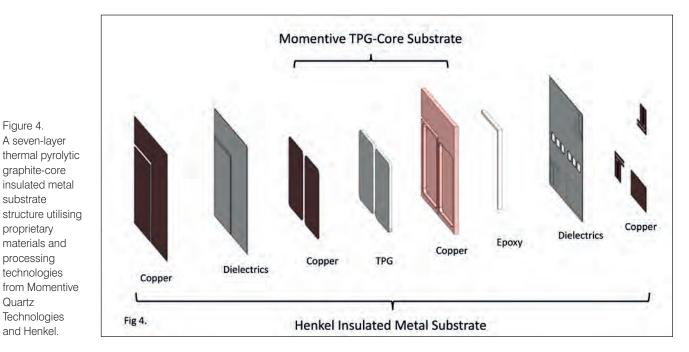

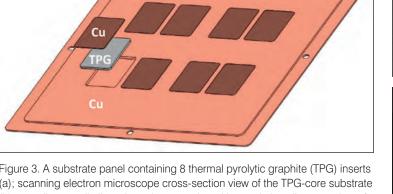

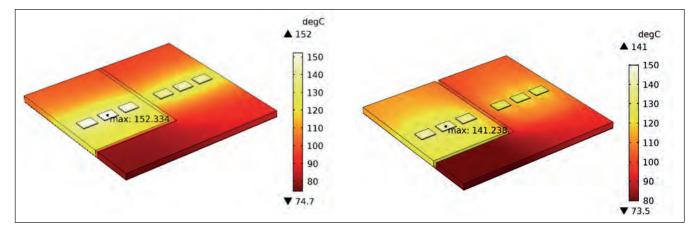

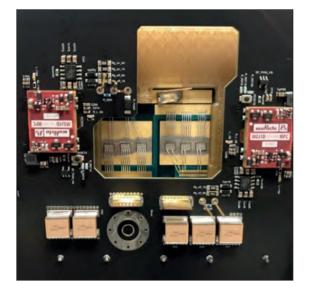

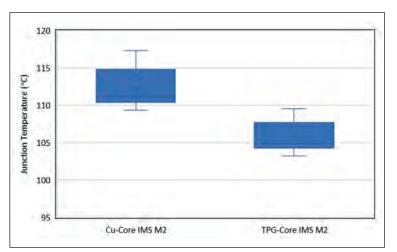

#### 48 Unlocking the potential of SiC power modules with graphite

Replacing the copper core in insulated metal substrates with highly oriented graphite boosts thermal conductivity of the SiC power module while trimming its weight

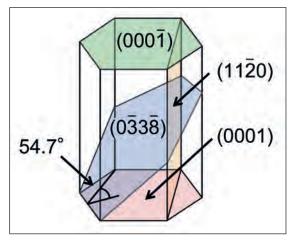

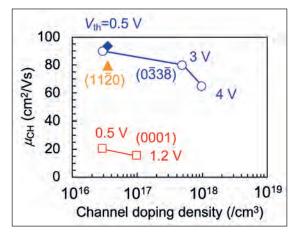

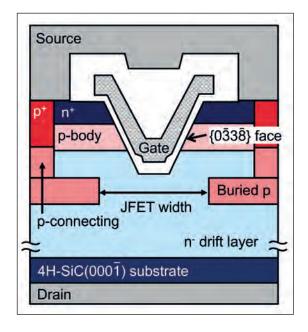

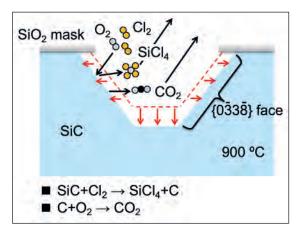

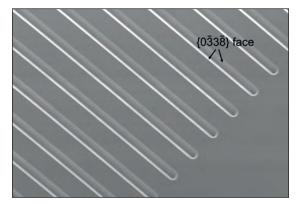

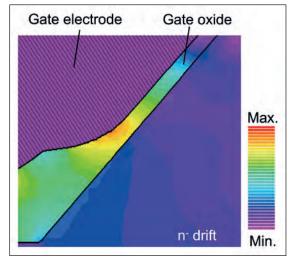

## 54 A better face for the SiC MOSFET

SiC MOSFETs with a V-grooved trench reduce onresistance and trim switching losses

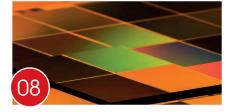

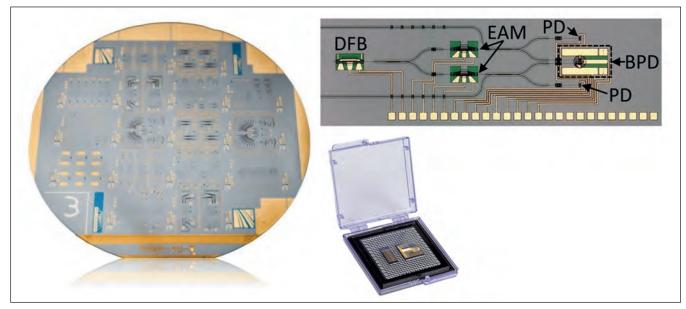

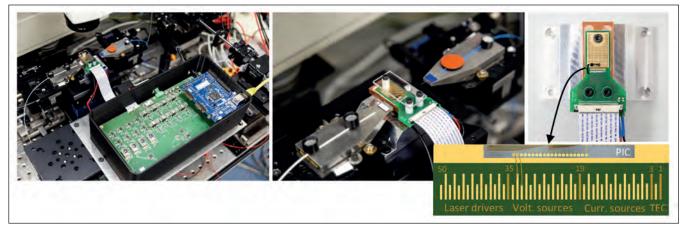

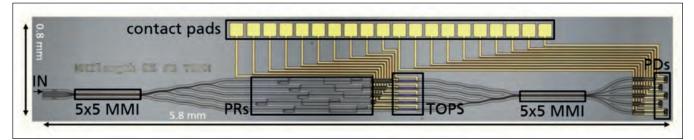

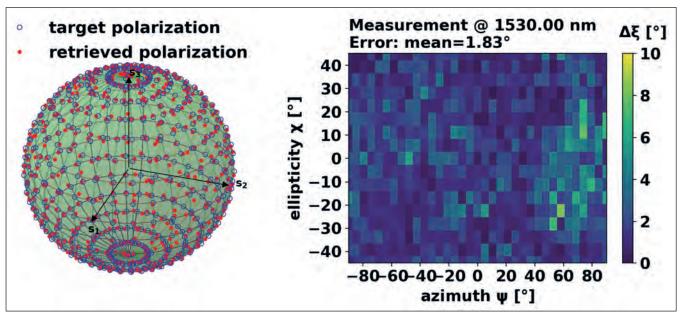

## 60 Plug and play characterization

An integrated electrical test platform builds on the advantages of foundry services by offering chip-level test and characterization

#### news

52

- 06 Transphorm and Magneti Marelli sign partnership

- 07 Nexperia partners with Ricardo on GaN-based EV inverter for electric vehicles

- 08 EVG opens heterogeneous integration centre

- 09 SK Siltron acquires DuPont SiC wafer division

- 10 Xiaomi chooses Navitas GaN chips for phone charger

- Vixar launches high efficiency multi-Junction VCSEL

- 12 Infineon announces 650 V SiC MOSFETs

#### news analysis

## 14 RF GaN: big revenues, bright future?

Despite billion dollar revenues forecast to roll in from 5G infrastructure and defence in just three years, GaN may not have hit the big-time quite yet

## 16 Qromis: ready for business

As the GaN market gathers momentum, Qromis is serving up fab-friendly substrates and epiwafers to ease device manufacture

## 18 EpiPix: a new way with microLEDs

University of Sheffield spin-out, EpiPix, is set to deliver the ultrahigh brightness, ultra-small microLED arrays that industry players crave

#### research review

#### 66 Longer lasting UVC LEDs

A reduction in oxygen levels is believed to be behind a substantial increase in the lifetime of UVC LEDs

#### 68 Building brighter red LEDs

Switching the substrate for the growth of red-emitting nitride LEDs from sapphire to gallium oxide increases the efficiency of the emitter

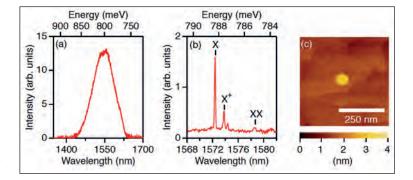

#### 69 Droplets spawn singlephoton sources

Dots formed by droplet epitaxy and high-temperature crystallisation produce singlephoton emission at a telecom transmission window

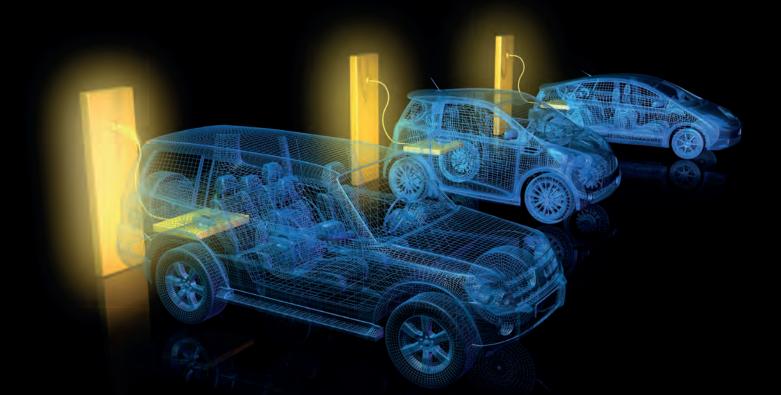

## Transphorm and Magneti Marelli sign partnership

ITALIAN AUTOMOTIVE supplier Magneti Marelli and US GaN company Transphorm have signed a partnership agreement for developing power converters, onboard chargers and inverters for electric and hybrid vehicles.

Working alongside Transphorm engineers, Marelli engineers will be able to use their experience to advise on product development relevant to its ongoing investment in the development of e-powertrain solutions for electric vehicles and also for motorsport applications. For such joint development and coworking of engineers, Transphorm will exclusively cooperate with Marelli for two years, to enable the development of new technologies for electric vehicles.

Joachim Fetzer, CEO, electric powertrain, Marelli, said: "Electric Vehicle power conversion is fundamentally important to the future of electric vehicles and investment in technologies like this are critical to ensure the very highest performance of electric vehicles at a lower cost. We are delighted to partner with Transphorm, who are true leaders in the market.

Fetzer added: "This partnership allows us to work with the Transphorm team to shape and improve products that will ultimately ensure improved performance, efficiency of power electronics and ultimately lower the cost of electric vehicles."

Primit Parikh, co-founder and COO, Transphorm, said: "Automotive and EVs represent one of the largest opportunities for GaN in power conversion and our partnership with a global leader like Marelli is a strong testament to the quality, reliability, manufacturing and overall product performance of our GaN solutions.The long-term innovative system level vision of the Marelli Electric Powertrain team will be extremely valuable in furthering GaN in the electric vehicle."

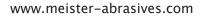

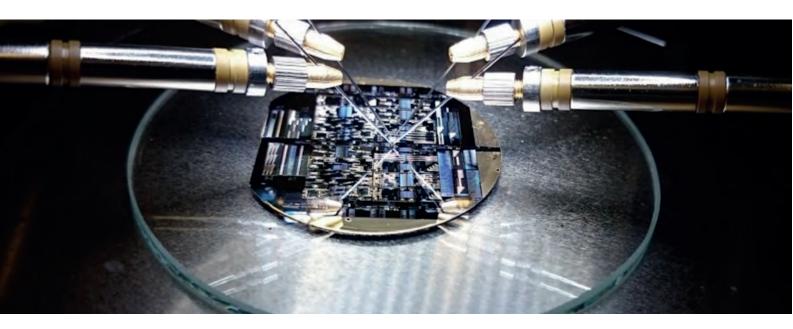

### Imec and CST Global integrate InP light sources

BELGIAN research hub Imec and CST Global, a UK-based designer and manufacturer of III-V compound semiconductors for photonics products, announce the successful integration of InP distributed feedback (DFB) lasers from CST Global's InP100 platform into Imec's integrated silicon photonics platform.

Interfaces for hybrid integration of InP DFB lasers and reflective semiconductor optical amplifiers (RSOA) will become available as part of Imec's silicon photonics prototyping services in the first half of 2021, following further optimisation and qualification work in 2020. This joint Imec-CST Global technology offering is expected to boost the adoption of silicon photonics in cost-sensitive applications, including optical interconnects, sensing, computing and beyond.

Silicon photonics technology has made great progress over the past decades and is used extensively in a variety of applications – from fiber-optic communications to sensing. Technology platforms have evolved into mature vehicles and are available to industry and academia for prototyping, low-volume and higher-volume manufacturing. But a widely available, cost-effective solution to integrate light sources in silicon photonic chips has been missing, hampering the adoption of silicon photonics in costsensitive markets. As silicon does not emit light efficiently, light sources made of III-V semiconductors are typically implemented as separately packaged components. Such external light sources typically suffer from higher coupling loss; a large physical form factor; and a substantial packaging cost.

Imec has recently joined forces with CST Global to extend Imec's silicon photonics technology portfolio with passively assembled, edge-emitting, InP DFB lasers and InP RSOAs. This collaboration, which started in 2019, has now resulted in the first successful assemblies of C-band (1530-1565 nm) InP DFB lasers onto Imec's platform. The InP lasers were 'flip-chip' integrated onto the silicon photonic circuits through a die-to-die bonding process, aligning efficiently and coupling more than 5 mW into the SiN waveguides on the chip.

Joris Van Campenhout, program director optical I/O at Imec: "We are excited

to work with CST Global to extend Imec's silicon photonics portfolio with hybrid integrated InP light sources. Our first passive laser assemblies have demonstrated excellent initial results."

"Throughout 2020, we will further optimise the precision and throughput of the laser assembly process; extend the functionality to include RSOA integration at 1310/1550 nm wavelengths; and perform reliability qualification. We expect that the availability of these hybrid, integrated light sources will boost industrial uptake of silicon photonics devices in a variety of costsensitive markets. Early access through Imec's iSiPP200 prototyping services is anticipated by the first half of 2021."

Antonio Samarelli, integration manager at CST Global: "We are extremely pleased to be working with Imec on this project. The hybrid integration of InP light sources (DFBs and RSOAs), designed and fabricated on CST's InP100 manufacturing platform, combined with the iSiPP platform allow the creation of powerful photonic integrated circuits for advanced components with improved performance and lower cost in the future."

CST Global will continue to work closely with Imec to extend the functionality and capabilities of the InP100 platform to meet the InP light source requirements of novel, advanced PICs for high volume commercial applications.

news review

# Nexperia partners with Ricardo on GaN-based EV inverter for electric vehicles

NEXPERIA, a maker of discretes, MOSFETs and GaN FET components and analogue and logic ICs, has announced a partnership with automotive engineering consulting company, Ricardo, to produce a technology demonstrator for an EV inverter based on GaN technology.

GaN is the preferred switch for these applications as GaN FETs lead to systems with greater efficiencies at lower costs with improved thermal performance and simpler switching topologies. In automotive terms this means that the vehicle has a greater range – the major concern for anyone looking to buy an electric vehicle. GaN is now on the brink of replacing silicon based IGBTs and SiC as the preferred technology for the traction inverters used in plug-in hybrids or full battery electric cars.

Nexperia announced a range of AEC-Q101-approved GaN devices last year, providing automotive designers with an ever-widening portfolio of proven, reliable devices in this high-efficiency technology, providing the power density required for electrification of the powertrain.

Ricardo is very well regarded in the automotive industry. This global engineering innovation company designs and consults on concepts within the automotive industry, including the manufacture of prototypes and demos, and boast collaborations with high-profile leading brands such as McLaren and Bugatti. Ricardo was the perfect partner for Nexperia for this project.

Michael LeGoff, general manager GaN, Nexperia: "By designing our GaN devices into an inverter and trialling them through Ricardo, we will be able to better understand how a vehicle can be driven safely and reliably. We are developing a real solution that I think a lot of automotive designers will be interested in having a look at and will find extremely advantageous."

Adrian Greaney, director technology & products, Ricardo: "Semiconductor technology is key to the efficiency of the inverter system and the role that it plays in the performance and efficiency of an electrified vehicle. By delivering significant benefits in terms of the switching speed and efficiency, gallium nitride is a real enabling technology. As well as leading to increased range, it allows us to reduce the package size and weight of the inverter, which provides greater powertrain design flexibility as well as contributing to vehicle mass reduction. There are also many associated benefits when we look at the design from a system level, and Ricardo is therefore pleased to be collaborating with Nexperia on GaN devices."

## EVG opens heterogeneous integration centre

EV Group (EVG), a supplier of wafer bonding and lithography equipment for the MEMS, nanotechnology and semiconductor markets, has established the Heterogeneous Integration Competence Centre, which is designed to assist customers in using EVG's process solutions and expertise to enable new and enhanced products and applications driven by advances in system integration and packaging.

The Heterogeneous Integration (HI) Competence Centre combines EVG's wafer bonding, thin-wafer handling, and lithography products and expertise, as well as pilot-line production facilities and services at its state-of-the-art cleanroom facilities at EVG's headquarters in Austria, supported by EVG's worldwide network of process technology teams. "Heterogeneous integration fuels new packaging architectures and demands new manufacturing technologies to support greater system and design flexibility, as well as increased performance and lower system design costs," stated Markus Wimplinger, corporate technology development & IP director of EV Group.

"EVG's new HI Competence Centre provides an open access innovation incubator for our customers and partners across the microelectronics supply chain to collaborate while pooling our solutions and process technology resources to shorten development cycles and time to market for innovative devices and applications enabled by heterogeneous integration."

EVG has an extensive background in heterogeneous integration, providing solutions for this technology trend for more than 20 years.

Among these are: permanent wafer bonding – including direct fusion and hybrid bonding for 3D packaging and metal bonding – and die-to-wafer bonding with and without collective carriers for integration of III-V compound semiconductors and silicon as well as high-density 3D packaging; temporary bonding and debonding, including mechanical, slide-off/lift-off, and UV laser assisted; thin-wafer handling; and innovative lithography technologies, including mask aligners, coaters and

developers, and maskless exposure/ digital lithography. In the field of permanent bonding, EVG pioneered the patented SmartView wafer-to-wafer alignment system more than 20 years ago, and has refined this technology over the years to support breakthrough technology advances such as backsideilluminated CMOS image sensors and more recently the first demonstration of sub-100-nm wafer-to-wafer alignment overlay for hybrid bonding - enabling devices such as 3D backside-illuminated CMOS image sensors and memory-onlogic stacking. EVG developed the first temporary bonding systems for ultrathin wafers as early as 2001, which are essential for 3D/stacked die packaging, as well as revolutionised low-temperature laser de-bonding for ultra-thin and stacked fan-out packages.

In lithography, EVG says that it cemented its position as a recognised technology leader with the delivery of the first UV moulding solutions for high-volume production of wafer-level optics more than a decade ago, and has since led the proliferation of nanoimprint lithography to high-volume manufacturing.

EVG continues to break speed and accuracy barriers in mask alignment lithography for advanced packaging and, more recently, unveiled the world's first highly scalable maskless exposure technology, which addresses emerging requirements in high-volume manufacturing back-end lithography.

#### Qorvo completes custom MMIC acquisition

QORVO has completed its acquisition of Custom MMIC, a supplier of highperformance GaAs and GaN monolithic microwave integrated circuits (MMICs) for defence, aerospace and commercial applications.

As part of Qorvo's Infrastructure and Defense Products business, the Custom MMIC team will continue to expand its millimetre-wave capabilities for products used in defence phased array and AESA radars, electronic warfare, satellite communications, wireless backhaul and microwave test equipment. James Klein, president of Qorvo Infrastructure & Defense Products said, "Custom MMIC's best-in-class die and packaged components augment our power amplifiers to enable multi-chip modules for a broad range of defense, aerospace and commercial applications."

"We look forward to building on Custom MMIC's reputation as an outstanding strategic supplier to leading defense prime customers, as we expand our millimetre-wave capabilities and product offerings for defense and commercial markets, including 5G." Chelmsford, Massachusetts-based Custom MMIC was founded in 2006 and has extensive experience developing MMICs at frequencies up to 70 GHz.

Custom MMIC adds small signal millimetre-wave expertise and a portfolio of more than 180 standard products including LNAs, mixers, attenuators, phase shifters and switches.

Custom MMIC president and CTO Paul Blount joins Qorvo as a director of engineering for Infrastructure and Defense Products.

news review

## SK Siltron acquires DuPont SiC wafer division

SK SILTRON, a maker of semiconductor wafers, has completed the acquisition of DuPont's SiC wafer unit. The acquisition was decided through a board meeting in September and closed on February 29.

The \$450 million acquisition is to meet the demand from consumers and governments for sustainable energy and environmental solutions. SK Siltron will continue to invest in related fields even after the acquisition, which is expected to increase SiC wafer's production and create additional jobs in the US. The primary site for the business is in Auburn, Michigan, about 120 miles north of Detroit, USA. Through this acquisition, SK Siltron, based in Gumi, South Korea, is expected to maximise its R&D and production capabilities and synergy between its current major businesses, while securing new growth engines by entering rapidly expanding areas.

SK Siltron is South Korea's only producer of semiconductor silicon wafers and one of the top five global wafer manufacturers with annual sales of 1.542 trillion won, accounting for about 17 percent of global silicon wafer sales (based on 300 mm). To sell silicon wafers, SK Siltron has overseas subsidiaries and offices in five locations – the United States, Japan, China, Europe and Taiwan. The US subsidiary, established in 2001, sells silicon wafers to eight customers, including Intel and Micron.

SK Siltron is an affiliate company of Seoul-based SK Group, South Korea's third-largest conglomerate. SK Group has made North America a global hub, with its investments in the US in batteries for electric vehicles, biopharmaceuticals, materials, energy, chemicals and ICT, reaching \$5 billion in investments in the US over the past three years.

#### STMicroelectronics and TSMC Collaborate on GaN

STMICROELECTRONICS and TSMC, the world's largest dedicated foundry, are collaborating to accelerate the development of GaN process technology and the supply of both discrete and integrated GaN devices to market. Through this collaboration, ST's GaN products will be manufactured using TSMC's GaN process technology.

Power GaN and GaN IC technologybased products will enable ST to provide solutions for medium- and high-power applications with better efficiency compared with silicon technologies on the same topologies, including automotive converters and chargers for hybrid and electric vehicles. Power GaN and GaN IC technologies will help accelerate the trend of the electrification of consumer and commercial vehicles. "As a leader in both wide bandgap semiconductor technology and in power semiconductors for the demanding automotive and industrial markets, ST sees significant opportunity in accelerating the development and delivery of GaN process technology and bringing power GaN and GaN IC products to the market. TSMC is a trusted foundry partner that can uniquely meet the challenging reliability and roadmap evolution requirements of ST's target customers," said Marco Monti, president of STMicroelectronics' Automotive and Discrete Group.

"This cooperation complements our existing activities on power GaN undertaken at our site in Tours, France and with CEA-Leti. GaN represents the next major innovation in power and smart power electronics, as well as in process technology," said Kevin Zhang, Vice President of Business Development at TSMC. "We look forward to collaborating with ST and bring the applications of GaN power-electronics to Industrial and Automotive Power Conversion".

"TSMC's leading GaN manufacturing expertise, combined with STMicroelectronics' product design and automotive-grade qualification capabilities, will deliver great energy efficiency improvement for industrial and automotive power conversion applications that are more eco-friendly and help accelerate the electrification of vehicles."

ST expects the delivery of first samples of power GaN discrete devices to its key customers later this year, followed by GaN IC products within a few months.

## Xiaomi chooses Navitas GaN chips for phone charger

NAVITAS SEMICONDUCTOR has announced that its GaNFast charging technology had been adopted by Xiaomi for the flagship Mi 10 PRO smartphone. It now takes only 45 minutes to charge the Mi 10 PRO from 0 to 100 percent.

Xiaomi's 65 W GaN charger uses Navitas' NV6115 and NV6117 GaNFast power ICs which are optimised for high-frequency, soft-switching topologies. Monolithic integration of FETs, drivers and logic delivers a small, fast, 'digital-in, powerout' power conversion module. Using GaNFast, Xiaomi's 65 W GaN charger is only 56.3 mm x 30.8 mm x 30.8 mm, which is half the size of standard adapters.

"GaN as a new semiconductor material has brought unimaginable effects to the charger," said Jun Lei, Xiaomi chairman and CEO. "It enables the charger to become extremely small and the charging efficiency extremely high. The 65 W GaN charger is only half the size of the 65 W traditional charger that comes as standard with our Xiaomi 10 PRO."

Xiaomi invested earlier in Navitas Semiconductor to lay the groundwork for

this cooperation, which has also enabled Navitas Semiconductor to broaden its sales channels.

Gene Sheridan, CEO of Navitas Semiconductor, said: "I am very pleased to see Xiaomi's open attitude towards new materials and new technologies. From the start, Navitas has focused on the technology application and innovation of GaN materials."

"GaNFast power ICs are monolithic integration of FET, drive and logic and achieve extremely small application size and high efficiency. For manufacturers who want to lead with technology, GaNFast enables high performance and drives product differentiation."

Yingjie Zha, general manager of Navitas Semiconductor China, said: "The battery capacity of smartphones, tablets and laptops is increasing, while consumers are eager to have a faster-charging experience. GaNFast technology has the advantages of small size, light weight and high efficiency, which makes it extremely attractive."

"GaNFast technology brings the industry a small, efficient charger that can quickly charge electronic products such as mobile phones and laptops."

#### TMD takes share in GaN PA specialist diamond microwave

Diamond Microwave Limited, a UK-based technology specialist in high-performance microwave power amplifiers, has announced that TMD Technologies, a London-based manufacturer of high-performance equipment for the microwave industry, has become a shareholder in DML.

Diamond Microwave has been a pioneer in the development and manufacture of advanced compact GaN-based microwave highpower solid-state power amplifiers for the radar, electronic warfare, communications and aerospace sectors. DML's chip and wire GaN technology is particularly suited to these demanding applications, where their power-tovolume performance is a leading-edge capability differentiator.

DML's CEO, Richard Lang commented:

"We are delighted to welcome TMD as an investor. This is a welcome step in enhancing our existing relationship and further developing our joint interests in world-class amplifier products. TMD is an ideal partner for DML, bringing the possibility of new channels through which to develop and exploit our solidstate power amplifier technology."

Dave Brown, TMD's Group CEO, added: "We have been collaborating

with Diamond Microwave for several years and are very pleased with this latest development, which is a logical step forward in our business relationship. Their specialised technological expertise has proved particularly successful across the aerospace and defence industries and complements our current technologies targeted at this market sector. We are looking

forward to increased involvement with this forward-looking company – to our mutual benefit".

Celebrating the partnership with a virtual meeting are (left to right): Howard Belk, engineering director, Diamond Microwave; Richard Lang, CEO, Diamond Microwave; Dave Brown, group CEO, TMD Technologies; Nigel Hann, sales director, TMD Technologies Ltd.

## Vixar launches high efficiency multi-junction VCSEL

VIXAR, a subsidiary of Osram, has launched its multi-junction VCSEL technology.

The new multi-junction VCSEL boasts a world-record 60 percent power conversion efficiency at 940 nm, significantly higher than the singlejunction performance of 53 percent.

The new multi-junction technology is said to represents the next leap forward for the VCSEL industry. The technology can be applied to products in the company's portfolio and boasts slope efficiencies of 2 W/A in dual junction and 3 W/A in triple junction. It offers a worldrecord 60 percent power conversion efficiency — significantly higher than the comparable single-junction's performance of 53 percent peak wallplug efficiency.

Greater efficiency reduces the overall thermal load. Higher power density leads to a reduced chip and package size, enabling simpler optic designs and system architecture.

The higher slope efficiency means that a much lower pulsing forward current is required to reach the same optical power as a single-junction VCSEL. The advantage for customers is greatly reducing the current required, which improves the switching speed of the driver. This reduction of current allows the VCSEL to deliver a remarkable one nanosecond pulse for tens or even hundreds of watts.

"Our record-setting multi-junction technology now puts us in a leading position in the VCSEL market" said Klein Johnson, co-founder and CTO of Vixar.

"Our VCSEL technology solves a critical need for customers and is poised to play a key role in shaping the next generation of consumer, industrial and automotive applications."

#### STMicroelectronics to acquire majority stake in Exagan

STMicroelectronics has signed an agreement to acquire a majority stake in French GaN innovator Exagan. Exagan's expertise in epitaxy, product development and application know-how will broaden and accelerate ST's power GaN roadmap and business for automotive, industrial and consumer applications. Exagan will continue to execute its product roadmap and will be supported by ST in the deployment of its products.

Terms of the transaction were not disclosed and closing of the acquisition remains subject to customary regulatory approvals from French authorities. The signed agreement also provides for the acquisition by ST of the remaining minority stake in Exagan 24 months after the closing of the acquisition of the majority stake. The transaction is funded with available cash.

"ST has built strong momentum in SiC and is now expanding in another very promising compound material, GaN, to drive adoption of the power products based on GaN by customers across the automotive, industrial and consumer markets" said Jean-Marc Chery, president and CEO of STMicroelectronics.

"The acquisition of a majority stake in Exagan is another step forward in strengthening our global technology leadership in power semiconductors and our long-term GaN roadmap, ecosystem and business. It comes in addition to ongoing developments with CEA-Leti in Tours, France, and the recently announced collaboration with TSMC."

Founded in 2014 and headquartered in Grenoble (France), Exagan is dedicated to accelerating the power-electronics industry's transition from silicon-based technology to GaN-on-silicon technology, enabling smaller and more efficient electrical converters. Its GaN power switches are designed for manufacturing in standard 200 mm wafer fabs.

#### Advanced Compound Semiconductor Foundry Services

MOCVD · Fabrication · Testing

Advanced III-V semiconductor solutions for optoelectronics application in the biotechnology, telecommunications, energy, industrial, and defense industries.

MasimoSemiconductor.com | 603-595-8900

## Infineon announces 650 V SiC MOSFETs

INFINEON TECHNOLOGIES is expanding its SiC product portfolio with 650 V devices. With the newly launched CoolSiC MOSFETs the company says that it is addressing the growing demand for energy efficiency, power density, and robustness in a wide range of applications. Amongst them are server, telecom and industrial SMPS, solar energy systems, energy storage and battery formation, UPS, motor drives as well as EV-charging.

"With this launch, Infineon complements its broad silicon, SiC, and GaN-based power semiconductor portfolio in the 600 V / 650 V power domain," said Steffen Metzger, senior director high voltage conversion at Infineon's Power Management & Multimarket Division. "It underlines our unique position in the market being the only manufacturer with such a broad offering for all three power technologies. Additionally, the new CoolSiC family supports our claim to be the number one supplier of SiC MOSFET switches for industrial purposes."

The CoolSiC MOSFET 650 V devices are rated from 27 m $\Omega$  to 107 m $\Omega$ . They are available in classic TO-247 3-pin as well as TO-247 4-pin packages, which allows for even lower switching losses. As for all

previously launched CoolSiC MOSFET products, the new family of 650 V devices are based on Infineon's state-of-the-art trench semiconductor technology.

Maximising the strong physical characteristics of SiC, this ensures that the devices offer superior reliability, best-in-class switching and conduction losses. Additionally, they feature highest transconductance level (gain), a threshold voltage of 4 V and short-circuit robustness.

650 V CoolSiC MOSFETs are said to offer many benefits in comparison to other silicon and SiC solutions such as switching efficiency at higher frequencies and high reliability. Thanks to the low on-state resistance dependency on temperature they feature an excellent thermal behaviour. The devices also have body diodes retaining a low level of reverse recovery charge, roughly 80 percent less than the best superjunction CoolMOS MOSFET.

The commutation-robustness helps in achieving, very easily, an overall system efficiency of 98 percent, such as through the usage of continuous conduction mode totem-pole power factor correction (PFC).

To ease the application design using CoolSiC MOSFETs 650 V and to ensure high performance operation of the devices, Infineon offers dedicated 1-channel and 2-channel galvanically isolated EiceDRIVER gate-driver ICs. This solution – combining CoolSiC switches and dedicated gate-driver ICs – helps lowering system costs as well as total cost of ownership and enables energy efficiency gains. The CoolSiC MOSFETs also work seamlessly with other ICs from Infineon's EiceDRIVER gate-driver family.

#### Qorvo launches highest-performance wideband GaN PA

QORVO has introduced what it believes is the world's highest-performance wideband power amplifier (PA). Designed for electronic warfare, radar and test instrumentation applications, the TGA2962 breaks through multiple performance barriers with an industryleading 10 W of RF power over the 2-20 GHz frequency range, 13 dB largesignal gain and 20-35 percent power added efficiency. This combination delivers the flexibility that system designers need to improve system performance and reliability while reducing component count, footprint and cost.

Roger Hall, General Mananger of Qorvo's High Performance Solutions business, said: "Qorvo has taken a significant step forward in the wideband space with the TGA2962, enhancing not just frequency range but every other performance aspect. No other company offers a single PA with this output power, bandwidth, power-added-efficiency and large signal gain."

The TGA2962 is built on Qorvo's GaN QGaN15 process technology. In addition, improved component integration – and use of a smaller driver amp enabled by the 13dB large-signal gain – result in a smaller device, making this a compelling solution for programmes that require size, weight, power and cost improvements.

Eric Higham, director of the Advanced Semiconductor Applications service and the Advanced Defense Systems service for Strategy Analytics, said: "The defence market, primarily radar and

communications applications, is seeing strong growth from new systems and major platform upgrades. This is also providing fuel for the GaN growth engine and should bode well for companies like Qorvo."

The TGA2962 wideband 10 W GaN PA is available now as a die to qualified customers.

## ACCELERATING HETEROGENEOUS INTEGRATION

VG

EV Group establishes Heterogeneous Integration Competence Center<sup>™</sup> to accelerate new product development fueled by heterogeneous integration and advanced packaging

Open access innovation incubator for EVG customers and partners across the microelectronics supply chain, guaranteeing the highest IP protection standards

Combining EVG's world-class wafer bonding, thin-wafer handling and lithography products and expertise, as well as pilot-line production facilities and services

Leveraging the state-of-the-art cleanroom facilities at EVG's headquarters in Austria, supported by EVG's worldwide network of process technology teams

**GET IN TOUCH** to discuss your manufacturing needs **HeterogeneousIntegration@EVGroup.com**

#### news analysis

## **RF GaN:** big revenues, bright future?

Despite billion dollar revenues forecast to roll in from 5G infrastructure and defence in just three years, GaN may not have hit the big-time quite yet, reports Rebecca Pool.

4G and 5G cell site base station

21++++

14 WWW.COMPOUNDSEMICONDUCTOR

#### news analysis

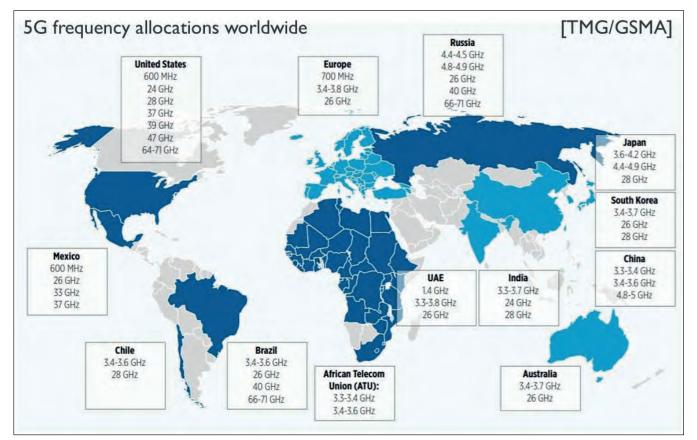

WHEN IT COMES to RF GaN, the future looks bright, according to the latest figures from Eric Higham, analyst, at Strategy Analytics. As he forecasts in *RF GaN Market Forecast: 2018 to 2023*, revenue for RF GaN-enabled devices grew by nearly 22 percent in 2018, and is set to surpass \$1.7 billion in 2023.

The drivers for this burgeoning growth come from 4G and 5G base station deployments, as well as defence applications. But the pathway to the billion dollar big-time may not be plain sailing.

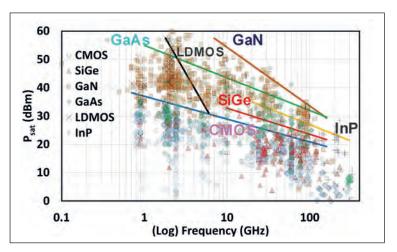

In the past, silicon-based laterally-diffused metal-oxide semiconductor (LDMOS) devices have been widely used in base station RF power amplifiers, but, as always, change is afoot. Since the beginning of 4G LTE deployment across China in 2014, equipment manufacturers and operators have embraced GaN with open arms, with the healthy revenue rises ensuing.

Given this, RF GaN has been steadily displacing LDMOS in base station power amplifiers. And while LDMOS technology still holds the largest revenue share right now, GaN is expected to continue to displace it, especially at higher frequency 5G deployments including millimetre-wave bands, from 30 GHz to 300 GHz.

But as Higham cautions, a 'storm cloud on the horizon' is looming for GaN RF power amplifiers in 5G base stations. In sub-6 GHz 5G spectrum bands, more and more radiators are set to be added to the antennas in massive MIMO systems, to ease beamforming.

"More radiators means you are more able to adapt, say, the shape of that beam, to make [data delivery] as efficient as possible for the operator," highlights Higham. "But as you add more and more radiators, the transmit power for each power amplifier goes down, which means SiGe and CMOS are now more inexpensive options [than GaN]."

And while GaN can offer, for example, greater poweradded efficiency and power density compared with the silicon-based technologies, operators have always tended to demand a lower power bill.

"Both GaN and silicon camps can make compelling arguments for their technologies but at the end of the day the market will choose," says Higham. "If an operators rolls out a 600 or 700 MHz 5G network, then that will likely have LDMOS in it due to its pricing." "LDMOS could remain the largest power technology for base stations in one, two, maybe three years," he adds. "However, the 5G spectrum mix of sub-6 GHz frequency versus high-frequency millimetre wave will be clearer in the next 18 months."

Infrastructure uncertainties are not the only cloud on GaN's horizon. Ongoing political tensions could also soften GaN growth in this market sector as China tech giant, Huawei, remains firmly fixed on the US Bureau of Industry and Security 'Entity List'.

"Huawei has been pretty proactive in adopting GaN, probably more so than other equipment suppliers," says Higham. "So if its market share goes down, then that could have an impact on GaN's market share."

What's more, China could well push ahead with growing its own compound semiconductor 'ecosystem', a move that would spell bad news for GaN players across the rest of the world. According to Higham, the Chinese government has poured billions into upgrading Sanan IC's compound semiconductor foundry while Huawei recently revealed a handset comprising components from domestic suppliers only.

"I don't know how good the Huawei phone is, and you can't build a foundry on Monday and have it up and running on Tuesday," says Higham. "But if China really pushes ahead to have a domestic capability then that will put a lot of other manufacturers at risk."

In the meantime, defence markets are set to provide respite from 5G infrastructure and political uncertainties. Thanks to a wave of defence programmes reaching production, major retrofits as well as procurements from US, China, Russia and other nations, Higham predicts the defence market will grow a little faster than the commercial sectors in the near-term. And, crucially, GaN has already proven itself in key defence market segments, radar and communications.

"The radar folk don't pull out a clean sheet of paper without writing GaN on it, and all the latest active electronically scanned array [antennas] use GaN," says Higham. "GaN is also being adopted very quickly in tactical radios and other communications applications that demand higher operating frequencies and bandwidths."

"So today, or at least until we see more certainty around 5G, the defence sector is safer than the infrastructure market," he adds.

## **Qromis:** ready for business

As the GaN market gathers momentum, Qromis is serving up fab-friendly substrates and epi-wafers to ease device manufacture, reports Rebecca Pool.

IN JANUARY THIS YEAR, Silicon Valley based Qromis revealed two developments that signal the company is on the cusp of rapid expansion.

news analysis

For starters, the fabless, wide bandgap materials business has just received an undisclosed investment from The Mirai Creation Fund, led by Japan-based investors SPARX.

At the same time, it has also signed a licensing agreement with Shin-Etsu Chemical, a Japanbased silicon wafer and materials manufacturer, to produce substrates and epiwafers for GaN power/RF electronics, LED devices and more.

Qromis' latest developments follow five years of development of its novel materials technology for substrates. And right now, chief executive, Cem Basceri, is excited.

"We've developed this unique CMOS fab-friendly substrate technology that is scalable and stressmatched to GaN," he says. "It sounds simple but it's taken years of development and investment."

"Now, a device manufacturer can take our substrate, and without any challenges, make many different device features," he adds. "This is extremely valuable."

#### Rapid progress

Qromis launched back in 2015 to commercialise its Qromis Substrate Technology, QST. Ready for GaN epi-growth, these substrates comprise an engineered coefficient of thermal expansion (CTE)-matched core onto which several engineered layers are deposited. A top thin silicon interface is also deposited onto the engineered layers.

Crucially, the CTE-matched core has a thermal expansion that closely matches the thermal expansion of the GaN-AlGaN epitaxial layers, enabling the deposition of low dislocation density, crack-free GaN epitaxy from a few microns to bulk-like thickness.

#### news analysis

As Basceri highlights: "We did this so that the substrate would be stress-matched with GaN without any cracking or wafer breakage issue and also to prevent substrate cross-talk in integrated circuits, which is a big issue on silicon."

Qromis has already released 6- and 8-inch GaN-ready QST substrates as well as 6- and 8-inch 'templates' with 5  $\mu$ m and 10  $\mu$ m GaN layers. What's more, 200 V and 650 V GaN HEMT epi-wafers, based on 6-inch and 8-inch QST substrates, are being fine-tuned for commercial devices while 900 V and 1200 V GaN HEMT epi-wafers are also being developed and sampled.

The company's rapid technology development follows partnerships and collaborations with a host of industry players up and down the supply chain. Within a year of launching, the company had partnered with Vanguard International Semiconductor, licensing its key technologies to the Taiwan-based silicon foundry for manufacturing.

Since 2016, the company has also worked closely with microelectronics innovation hub, imec, Belgium, on device fabrication, developing GaN power devices, in discreet and monolithically-integrated ICs forms, on 200 mm QST substrates in an advanced CMOS silicon pilot line.

Imec and Qromis have also been collaborating with GaN MOCVD equipment manufacturer, Aixtron, Germany, on GaN-on-QST epitaxy development. The results have been quite remarkable.

As Basceri points out, the industry standard platform for GaN-on-silicon has been 150 mm wafers. And while imec has pioneered the development of 200 mm GaN-on-silicon wafers for HEMTs to 650 V operating voltages, thermal mismatch between the GaN/AlGaN layers and silicon has stymied device fabrication at higher voltages.

Imec and Qromis have since developed enhancement mode p-GaN discrete and IC power devices on 200 mm QST substrates with epitaxy layers grown in Aixtron's G5+ C 200 mm MOVCD platform. Crucially, imec was able to port its p-GaN e-mode power device technology to Qromis' 200 mm GaN-on-QST wafers in its silicon pilot line, and also demonstrate highperformance power devices.

"Vanguard then decided to licence imec's device technology, GaN power epitaxy and processes and the company is currently manufacturing and tuning devices to [partner's] specifications," says Basceri. "This has been a big turning point."

Ramping manufacture In line with healthy GaN growth forecasts, Basceri says Vanguard will 'open its doors to everybody' later this year, offering GaN power, and later RF, device manufacturing services on the 200 mm diameter QST platform. This has also prompted the Qromis chief executive to establish a second manufacturing source for QST substrates and GaN-on-QST epitaxy wafers, in the form of Shin-Etsu Chemical. Importantly, with this partnership, QST-based materials products will be commercially available from both Shin-Etsu and Qromis for industry players.

According to Basceri, Shin-Etsu is going to aggressively move ahead with the development of GaN-related products, supplementing its existing line-up of GaN-on-silicon, SOI and silicon wafers. As he says: "From what we hear from our partners and customers that use Vanguard, we are expecting wafer demand to reach tens of thousands of wafers in the next three-to-four years."

With its substrates, Qromis will address a range of applications starting with GaN power and RF devices and later LED devices, such as microLEDs, and sensors. One of the key markets will be electric vehicles – as Basceri points out, a significant portion of SPARX's Mirai Creation Fund comes from Toyota Motor Corporation, which is heavily entrenched in this market.

"We expect to start ramping up 200 millimetre manufacturing between 2021 and 2022, and I would also expect to see an overall demand for 300 millimetre wafers starting by 2025 for which we have already started to receive some initial inquiries," says Basceri. "Several years ago, there were missing links in the GaN business, but the tipping point is now here."

Qromis, Chief Executive, Cem Basceri

# EpiPix: a new way with microLEDs

University of Sheffield spin-out, EpiPix, is set to deliver the ultra-high brightness, ultra-small microLED arrays that industry players crave. Rebecca Pool finds out more.

> EARLIER THIS YEAR, the UK-based University of Sheffield launched a spin-out company, EpiPix, to develop and commercialise microLED technology for display panels in augmented and virtual-reality devices, smart watches, mobile handsets and more.

Based on many years of GaN semiconductor research from Professor Tao Wang, based at the University's Centre for GaN Materials and Devices, the company has already demonstrated prototype micro-LED arrays on single wafers with microLED pixel sizes from 30  $\mu$ m down to 5  $\mu$ m and less.

The launch comes at a time when Apple has ploughed some \$2 billion into microLED development, myriad companies from Plessey and Glo to Lumens and Sharp have demonstrated microdisplays on CMOS backplanes, and patent fillings are going through the roof. EpiPix chief executive, Dennis Camilleri, is excited.

"We are already engaged in discussions with major end-user customers for AR/VR applications, manufacturers of smart watches and smart phones and also LiFi companies," he says.

"For many applications the key technical driver is to produce very small microLEDs that will give you that high resolution, high brightness display," he says. "We are going to produce less than five micron-size microLEDs and this is what all these major companies are interested in."

#### A direct approach

Your typical III-nitride microLEDs are manufactured using standard photolithography processes followed by dry-etching on a III-nitride LED wafer. However, dry-etching induces surface damage to the microLED, particularly at lower microLED diameters, degrading optical performance, including internal and external quantum efficiencies. As a result, industry players, far and wide, have struggled to fabricate high-brightness, microLEDs with dimension below 5  $\mu$ m.

Given this, Wang and colleagues decided to take a different tack and for the past five years have been developing a direct epitaxial method for fabricating ultra-small and ultra-bright InGaN micro-LEDs that eliminates the need for dry-etching.

Here an *n*-GaN layer is grown onto a silicon or sapphire substrate to create an as-grown *n*-GaN template. A SiO<sub>2</sub> film is then grown onto the *n*-GaN layer, with

Message

an array of holes of the required microLED shape and diameter. LED structures can then be grown onto this pre-patterned SiO<sub>2</sub> microhole arrayed template to form the microLED arrays.

Crucially, the method uses standard MOCVD processes, and the arrays are designed to be compatible with any existing microdisplay fabrication technique including, pick-and-place and mass transfer technologies. "Wang's process does not involve dry-etching, damage and optical degradation, and so we've been getting some very good external quantum efficiencies with our micro-LED arrays," says Camilleri. "This is why this process is attracting so much interest."

Indeed, earlier this year, Wang and colleagues unveiled high luminance green microLED array bare chips, with a diameter of 3.6  $\mu$ m, inter-pitch of 2  $\mu$ m and a record external quantum efficiency of 6 percent. This result has been quickly published in ACS Photonics. According to Camilleri, the researchers have fabricated blue microLEDs and are also developing red versions. EpiPix is also working with packaged chips.

"This figure of 6 percent for a very small green microLED is a world record," he says. "We are not using any reflective layers and no additional processing is taking place... This is pure light coming out of the microLED array."

So what now for EpiPix? As Camilleri points out, the start-up is operating on a commercial technology centre business model and will carry out product development, testing and validation of device performance, as demanded by end-user customers.

"EpiPix has a worldwide exclusive licence to commercially exploit the IP from the University of Sheffield... and when our customers scale up manufacturing of products based on our micro-LEDs, then EpiPix could licence IP out to them," he says. "We will be piloting assembly, production and packaging to ensure applications work but we don't see ourselves as a volume manufacturer of microLEDs."

EpiPix has a worldwide exclusive licence to commercially exploit the IP from the University of Sheffield... and when our customers scale up manufacturing of products based on our microLEDs, then EpiPix could licence IP out to them

So far, fabrication has taken place on 2-inch wafers, and now EpiPix will scale this to 4-inch or 6-inch substrates. The next 18 months to two years will also be spent on product development, beta prototyping, testing and providing samples to customers. And with process and device validation in hand, the microLED wafers will be ready for high-volume manufacture.

"These devices can also be used for high-speed data transmission in LiFi applications, but I expect the first applications to be AR and VR as well as smart watches and mobiles," says Camilleri. "In around two years, I want to be selling our microLED arrays to at least half a dozen global corporates in these applications."

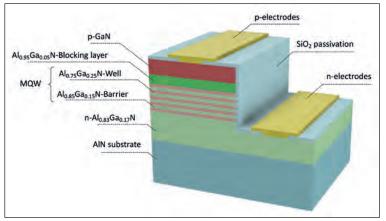

# A massive boost for **UV LED efficiency**

The monolithic integration of a conventional LED structure and a multiplicative photoelectric converter propels the wall-plug efficiency of deep UV LEDs emitting at 280 nm to more than 20 percent

#### BY HAIDING SUN FROM UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA AND HANLING LONG, FENG WU, JIANGNAN DAI AND CHANGQING CHEN FROM HUAZHONG UNIVERSITY OF SCIENCE AND TECHNOLOGY

FOR MANY DECADES, the most common source of UV light has been the mercury lamp. It has netted substantial sales, due to its widespread use in air/water purification, sterilization, phototherapy, lithography and UV curing. However, it is a source of UV emission that is far from ideal: it consumes much energy; lamps don't last long; and it contains mercury, which is toxic. The latter a big deal, as concerns over health continue to grow. For example, an international treaty known as the Minamata Convention on Mercury is calling for mercurycontaining products to be progressively prohibited by the end of this year.

A UV LED under operation

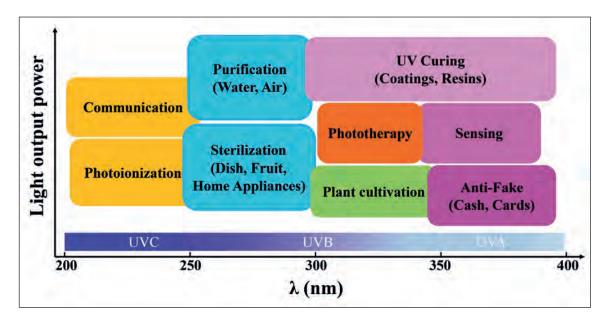

The leading environmentally-friendly, energy-efficient alternative to the mercury lamp is the UV LED. This

device, which is also renowned for its small size and long lifetime, spans a spectral range from 210 nm to 360 nm by varying the aluminium content in the AlGaN quantum wells. As well as offering an alternative to the UV lamp in some applications the UV LED can also be used for new tasks (see Figure 1). This helps the device to capture even more revenue. According to market analyst Yole Développement, the market size for the UV LED will grow from \$500 million in 2019 to \$1 billion in 2023.

The Achilles heel of the UV LEDs is its low efficiency. Compared to its blue cousins – which feature InGaN quantum wells, produce extremely high external quantum efficiencies and have a wall-plug efficiencies exceeding 80 percent – the performance of the UV LED is pitiful. As the wavelength drops below 360 nm efficiency plummets. For emission at 280 nm, the external quantum efficiency and wall-plug efficiency are typically just 6 percent and 5 percent, respectively.

It is possible to improve efficiency by refining the device. Efficiencies increase by: reducing defects and dislocations in the epilayers; improving *n*- and *p*-type doping efficiencies, to create conductive films for better current injection; re-designing the device for better light extraction; and employing a superior AlGaN-based quantum well and barrier design in the active region.

Our team from the University of Science and Technology of China and Huazhong University of Science and Technology has produced more efficient UV LEDs by making much progress on all these

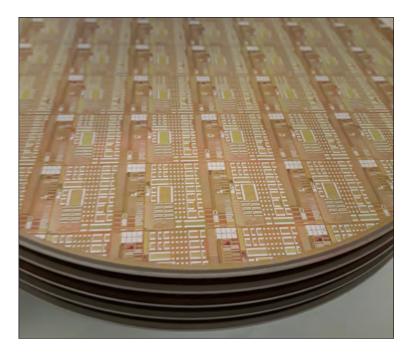

UV LEDs that smash the record for wall-plug efficiency are made on sapphire substrates

Figure 1. There are many applications for UV LEDs

fronts. However, this approach only gets us so far – so we have gone on to deliver a step change in performance by combining these refinements with a novel architecture that combines a conventional LED structure with a multiplicative photoelectric converter. Read on to discover the secrets of our success.

#### Conventional strategies

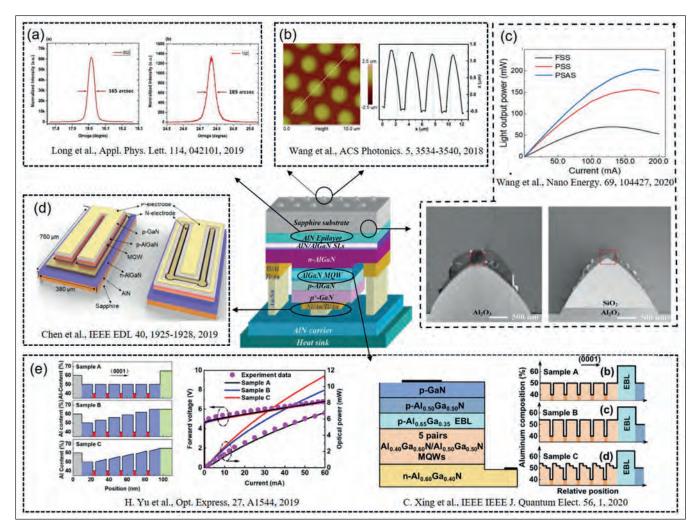

We grow our heterostructures for our UV LEDs on sapphire, a low-cost transparent substrate. We avoid native AIN because it is prohibitively expensive. The downside of sapphire is that is has lattice and thermal expansion mismatch with the nitride layers, leading to an inferior crystalline quality that drags down the radiative recombination efficiency. To tackle this issue, we have turned to pyramidal patterned sapphire, a foundation that supports lateral overgrowth during AIN epitaxy. The AIN films that result have excellent crystal quality. According to the full-width at halfmaximum of the peaks produced from X-ray diffraction rocking curves, the threading dislocation density is less than  $3 \times 10^8$  cm<sup>-2</sup> (see Figure 2 (a)). We have also undertaken reciprocal space mapping – this shows

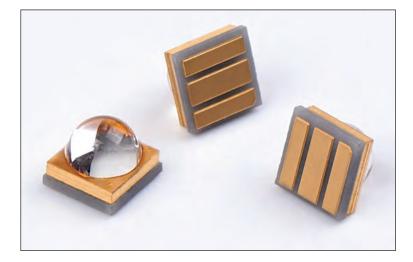

Packaged UV LEDs

that the epilayers are free from strain. Based on these findings, we know that we can supress the density of non-radiative recombination centres in the active region of our UV LEDs, and ultimately realise a high radiative recombination efficiency in these devices.

The benefits of patterning a substrate are not limited to the better material quality that comes from annihilation of dislocations. In addition, texturing boosts the output from the chip. This is particularly important in the deep UV, where the optical polarisation induced by the unique valance band structure within the active region limits the light extraction from the device. Unfortunately, the transverse-electric mode, which dominates in blue LEDs and aids extraction, is overtaken by the transverse-magnetic polarisation mode.

Previous work by our team has shown the benefits of using a moth-eye microstructure on sapphire's bottom surface of a flip-chip UV LED (see Figure 2(b)). With this pattern the uniformly periodic microstructure extends the light extraction angle. Note that this particular microstructure enhances the transverseelectric mode. It has a distribution with a dominate contribution in the vertical direction, which is easier to extract.

We realise an additional increase in light extraction by modifying light polarisation via strain modulation in the AlGaN quantum wells. By ensuring compressive in-plane strain in the wells we promote emission of the transverse-electric mode, leading to a hike in light-extraction efficiency for the UV LED.

Recently, we have made further gains by combining patterned sapphire with a silica array (see Figure 2(c)). This modification reduces threading dislocation density and enhances light extraction efficiency, thanks to a large difference in refractive index between the AIGaN epilayers and the patterned sapphire with a silica array. Another factor that governs the

Figure 2. Strategies to improve the performance of UV LEDs. (a) Patterned sapphire substrates enhance the crystal quality of epitaxy AIN. H. Long *et al.* Appl. Phys. Lett. **114** 042101 (2019) (b) Fabricating moth-eye microstructure on the sapphire bottom surface of flip-chip UV LEDs enlarges the light extraction angle. S. Wang *et al.* ACS Photonics **5** 3534 (2018) (c) Switching to a patterned sapphire with silica array (PSSA) reduces the threading dislocation density and enhances light extraction efficiency, thanks to the large refractive index contrast between the epilayers and PSSA. S. Wang *et al.* Nano Energy **69** 104427 (2020) (d) Novel electrode patterns can optimise current-spreading in a UV LED chip. Q. Chen *et al.* IEEE Elect. Dev. Lett. **40** 1925 (2019) (e) Designing the band structure of the AlGaN quantum wells heterostructure in the active region improves radiative recombination. H. Yu *et al.* Opt. Express **27** A1544 (2019); Ren *et al.* J. Phys. D Appl. Phys. **53** 073002 (2020)

performance of the UV LED is how efficiently the current can be injected into the device. As sapphire is insulating, it is impractical to adopt a vertical LED architecture. Due to this, the most common design for improving current injection and light extraction is based on a flip-chip bonding technology. Unfortunately, current crowding results, deteriorating device performance.

One option that we have developed for increasing the uniformity of current spreading in UV LED chips is to introduce novel electrode patterns (see Figure 2(d)). With this design, the *n*-type electrode surrounds its p-type counterpart to provide sufficient current paths for carrier transport.

Last but by no means least, UV LEDs are hampered by the strong spontaneous polarisation and the

piezoelectric polarisation field in the AlGaN material system. Due to the quantum confined Stark effect, the wavefunctions of the electron and hole are pulled in opposite directions, suppressing effective radiative recombination. To address this, a variety of forms of bandgap engineering have been pursued to increase the internal quantum efficiency, suppress the current leakage and diminish efficiency droop at high current injection (see Figure 2(e)).

Part of the reason behind the high quantum efficiency of blue LEDs is the indium segregation in the InGaN quantum wells. Segregation results in carrier localisation effects, increasing the likelihood of radiative recombination. With the AIGaN quantum wells required for UV LEDs, segregation is far less pronounced, because aluminium atoms have a far lower mobility than gallium. Localisation can also

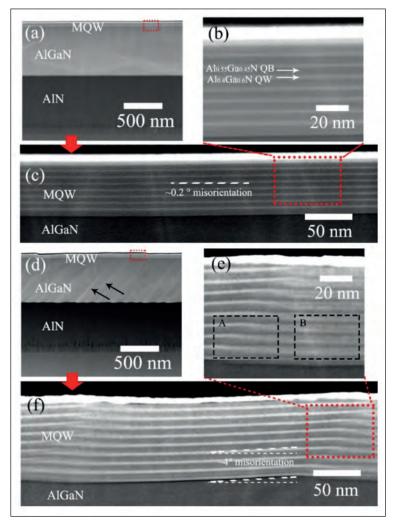

Figure 3. Cross-sectional scanning transmission electron microscopy image of AlGaN multi-quantum wells grown on (a-c) 0.2° and (d-f) 4° misoriented sapphire substrates. H. Sun *et al*. Adv. Funct. Mater. **29** 1905445 (2019)

result from thickness variations, but it is challenging to introduce, because aluminium and gallium atoms are a similar size.

The good news is that we are able to replicate the carrier localisation effects in blue LEDs in our UV emitters with a new kind of nanoscale structure, which we refer to as wavy quantum wells. We artificially create a 'phase separation', leading to compositional inhomogeneities in AlGaN alloys.

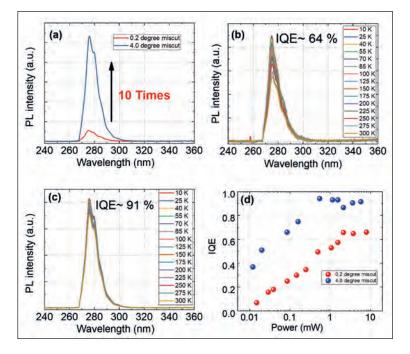

We produce LEDs with these wavy quantum wells by growing aluminium-rich deep UV LEDs on misoriented sapphire substrates with a significant mis-cut angle – it is as large as 4° (see Figure 3). The 280 nm LEDs produced by this process benefit from the semi-polar template that results – it produces a reduced polarisation field, in addition to increased carrier localisation.

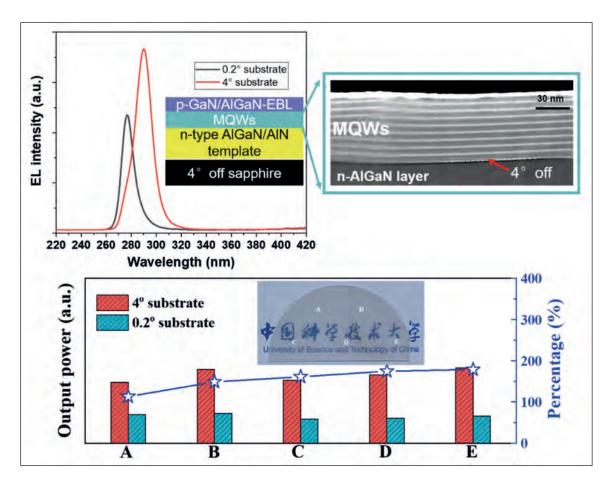

Measurements on these devices produce much better results than those made using flat sapphire. Photoluminescence intensity is at least ten times higher; internal quantum efficiency is six times higher at low excitation laser power, with a record result of over 90 percent; carrier lifetime is far longer, reaching 1.60 ns on 4° misoriented sapphire, compared with just 0.06 ns on 0.2° misoriented sapphire; and waferlevel output power of the UV LEDs is two-to-three times higher (see Figures 4 and 5).

Even with this improvement to the internal quantum efficiency of the UV LED, the wall-plug efficiency is typically below 5 percent for devices emitting below 300 nm. To reach far higher values requires a radical change to the design. We have done just that, realising a record wall-plug efficiency of 21.6 percent through the monolithic integration of a deep UV LED with a multiplicative photoelectric converter.

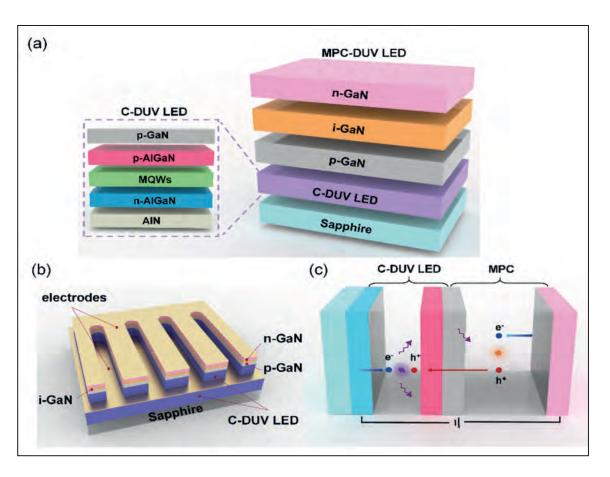

#### A radical architecture

Our novel device tackles the extremely low injection efficiency in conventional deep UV LEDs that is to blame for the unsatisfactory efficiency. In our radical design, the *p-i-n* GaN structure acts as an electricoptic converter and hole-multiplier, absorbing deep UV photons and generating electron-hole pairs. These carriers are pulled apart by the extremely high electric field. Holes are then multiplied by impact ionisation, before being re-injected into the active region, where they take part in radiative recombination (see Figure 6).

Left: Figure 4. (a) Room-temperature photoluminescence (PL) spectra of AlGaN multi-quantum wells (MQWs) grown on 0.2° and 4° sapphire substrates. Temperature-dependent PL spectra of AlGaN MQWs grown on (b) 0.2° and (c) 4° misoriented substrates. (d) Internal quantum efficiency (IQE) as a function of pumping power for both MQWs grown on 0.2° (red dots) and 4° (blue dots) misoriented substrates. H. Sun *et al.* Adv. Funct. Mater. **29** 1905445 (2019)

Figure 5. Electroluminescence (EL) spectra and output power comparison. H. Sun *et al.* Adv. Funct. Mater. **29** 1905445 (2019)

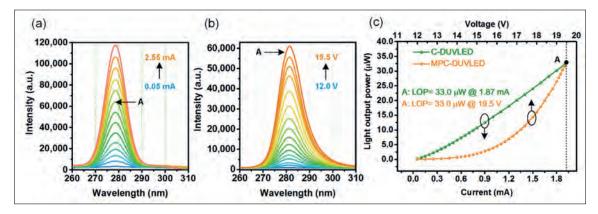

To investigate the photoelectric characteristics of our new device, we have compared its electroluminescence spectra to that of a conventional UV LED (see Figure 7(a) and (b)). Note that our new device exhibits a voltage-dependent characteristic, due to the reverse-biased multiplicative photoelectric converter. Plots of light output reveal an identical power when the conventional device is run at 4.88 V and 1.87 mA, and the novel LED is driven at 19.5 V and 7.85  $\mu$ A. From these figures we can conclude that the wall-plug efficiency in the conventional device is 0.36 percent, while that with the photoelectric converter is 21.6 percent – that is 60 times higher.

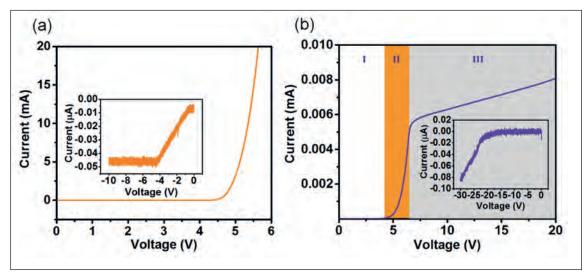

The current-voltage characteristics are markedly different from the norm in our novel device (see Figure 8). For our conventional UV LED, turn-on is at 4.5 V, while the leakage current is very low, indicating that it is reliable. In comparison, for our record-breaking LED, there are three distinct regions that span different ranges of operating voltage (for details, see Figure 8).

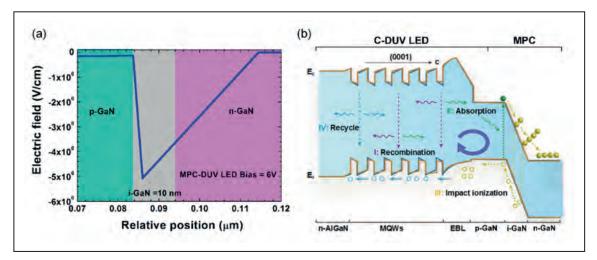

We have simulated the electric field profile of the p-*i*-n GaN region under a 6 V bias (see Figure 9(a)). Calculations reveal that the electric field extends into the n-GaN layer, and that the *i*-GaN layer is completely depleted. What's more, these simulations show that the strength of the electric field exceeds 5 MV/cm, making it strong enough to realise Geiger mode multiplication in GaN material.

Our modelling also offers an insight into the operation of our LED. When deep UV photons are absorbed within the device, they generate an electron hole pair, and due to the reverse bias in the multiplicative photoelectric converter, electrons drift to the anode and holes to the cathode. Due to Geiger mode, each carrier is multiplied several dozens of times in the multiplicative photoelectric converter, before it is re-injected into the active region. This results in a significant enhancement for the hole-injection efficiency in this class of LED. Photon recycling can also take place in this device (see Figure 9(b)) for details).

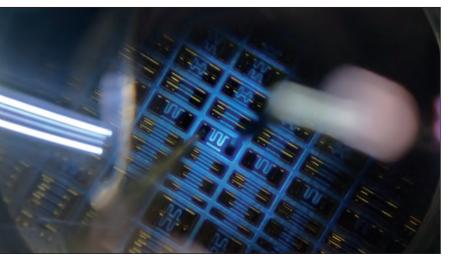

Material deposition for device fabrication

Figure 6. (a) The design of a conventional deep UV LED (C-DUV LED) and a multiplicative photoelectric converter deep UV LED (MPC-DUV LED). (b) Device structure of MPC-DUV LED. (c) An illustration of the carrier recombination and photon recycle process of the MPC-DUV LED. For more details see: S. Wang et al. Nano Energy. 66 104181 (2019).

The novel device that we have developed promises to realise far more than just a hero result in a lab. Its mass-production is not that difficult, as the multiplicative photoelectric converter can be grown *in-situ* using conventional MOCVD. The challenge is to improve the light output power of this form of LED.

Although there are applications where low-power deep UV LEDs can serve, such as microLEDs, many opportunities require sources with a high power. We are targeting this goal by optimising the epitaxial structure and fabrication process. While a 20 percent wall-plug efficiency is a very encouraging result, there is still much work to do. We hope that further increases in both the external quantum efficiency and the wall-plug efficiency are within our grasp by improving the material quality, the doping efficiency, and light extraction. Such efforts will take place during the on-going transition period from the mercury-based UV lamp to AlGaN-based UV LEDs, and will help to increase the adoption of clean, reliable UV sources. Given the rapid development in visible InGaN-based LEDs, all of us have good reason to be optimistic about the realisation of highly efficient, high-power deep UV LEDs in the near future.

Figure 7: Electroluminescence (EL) for (a) the conventional deep UV LED (C-DUV LED), and (b) the multiplicative photoelectric converter deep UV LED (MPC-DUV LED). (c) Light output power for the MPC-DUV LED and the C-DUV LED. More details are provide in: S. Wang *et al*. Nano Energy. **66** 104181 (2019).

Figure 8. Current-voltage characteristics of (a) a conventional deep UV LED (C-DUV LED) and (b) a multiplicative photoelectric converter deep UV LED (MPC-DUV LED). Insets show the reverse bias conditions. For region I and II, the curve is similar to that of the C-DUV LED, however, the current level is almost three magnitudes lower. For region III, which begins at 6.6 V, the current tendency changes abruptly, indicating minority carriers are effectively suppressed by the space charge region in the *p-i-n* GaN structure, and that the overall current may be limited by the reverse drift current. It may be attributed to the increase in the series resistance of the *p-i-n* GaN structure compared to region II. For more details please see: S. Wang *et al.* Nano Energy. **66** 104181 (2019).

Figure 9. (a) Electric field profile across the multiplicative photoelectric converter (MPC) structure in the MPC-deep UV LED at a 6 V bias. (b) The photon recycling, gain and output process for the MPC-DUV LED. In the initial recombination process I, half of the DUV photons propagate to the *n*-AlGaN layer and escape successfully, as shown by the purple arrows. The other half of the DUV photons propagate towards the MPC structure, and almost all are absorbed by the *i*-GaN layer of the MPC structure, indicated by the green arrows. DUV photons are absorbed and generate new electronhole pairs, as shown in process II. In process III, carriers are multiplied under Geiger mode, and collide with other atoms, ionising more carriers. The multiplied holes are re-injected into the multi-quantum wells (MQWs), and contribute to new radiative recombination, as shown in process IV. Note that for conventional DUV LEDs, only steps I and II take place. More details are provided in: S. Wang *et al.* Nano Energy. **66** 104181 (2019).

#### Further reading

H. Sun *et al.* Adv. Funct. Mater. **29** 1905445 (2019)

Ren *et al.* J. Phys. D Appl. Phys. **53** 073002 (2020)

H. Yu *et al.* Opt. Express **27** A1544 (2019)

S. Wang *et al.* Nano Energy **69** 104427 (2020)

- S. Wang et al. Nano Energy 66 104181 (2019)

- H. Long et al. Appl. Phys. Lett. 114 042101 (2019)

- Q. Chen et al. IEEE Elect. Dev. Lett. 40 1925 (2019)

- S. Wang et al. ACS Photonics 5 3534 (2018)

## **Comb lasers advance** high-performance computers

By tackling a bottleneck in bandwidth, multi-wavelength quantum dot lasers are enabling improvements in high-performance computers

#### BY GEZA KURCZVEIL, DI LIANG AND RAY BEAUSOLEIL FROM HEWLETT PACKARD ENTERPRISE

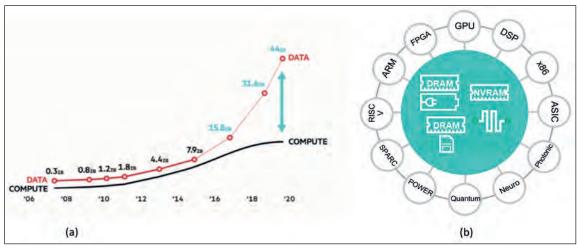

GROWTH IN DATA is occurring at a phenomenal rate. Now it takes just two years to produce 90 percent of all the data on the internet. That has major implications, particularly as it comes at a time when the performance of single cores has stagnated (see Figure 1 (a)).

To make headway, efforts are no longer directed at trying to increase the clock speed of single cores, but are focused on the construction of processors with more and more interconnected cores, and limited private memory on one socket. This new architecture makes much sense, given that memory is cheap, the opposite of what it was when the first computers were being built. In future, high-performance computers will feature a massive pool of memory at the centre, surrounded by many compute nodes located at the periphery, with all nodes having access to the full memory pool (see Figure 1 (b)).

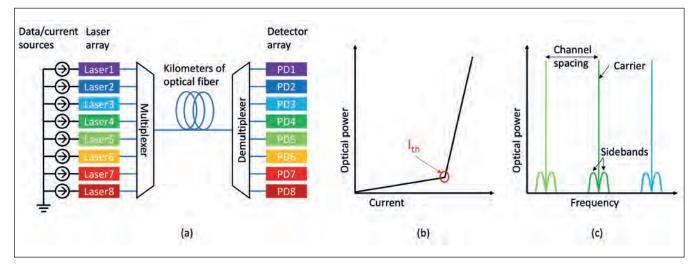

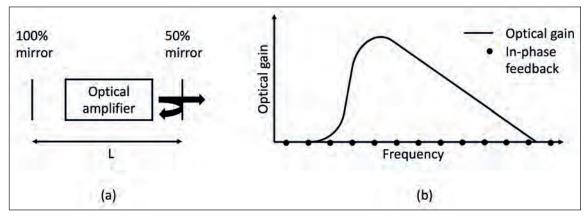

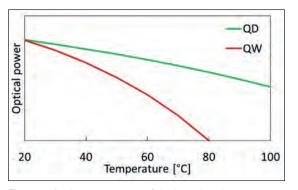

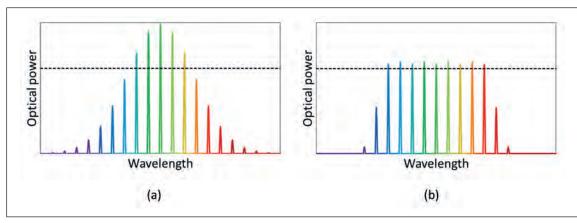

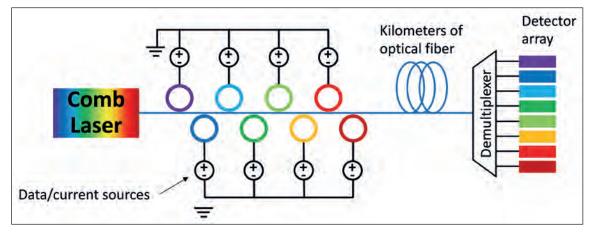

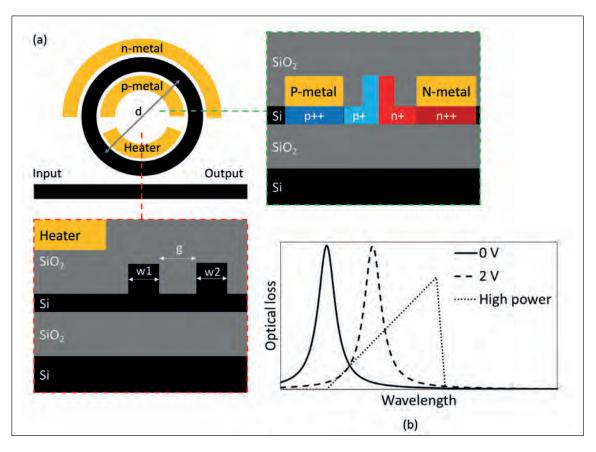

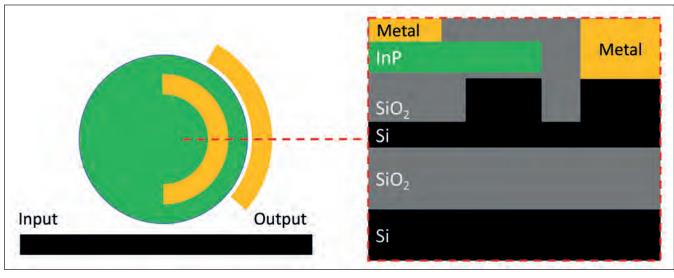

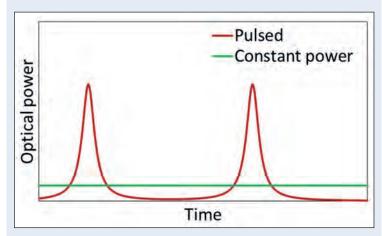

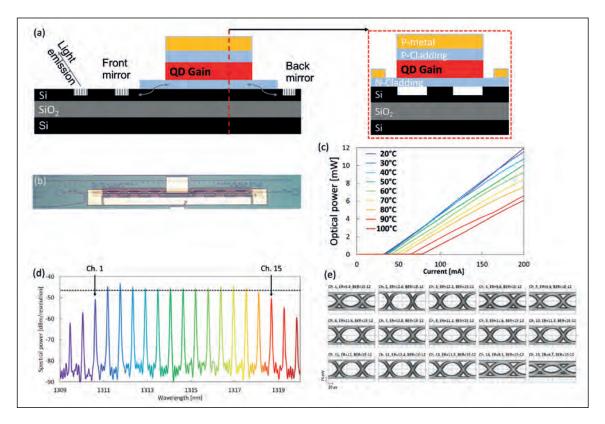

A key requirement for this new high-performance computer architecture is a massive communication link for the massive pool of memory. Without this, there would be insufficient throughput of data between memory and compute nodes.